當摩爾定律在2奈米節點逼近物理極限的同時,AI應用對系統整合的需求正呈指數級爆發,兩股力量的歷史性交匯催生了一個全新的競爭賽道。從台積電CoWoS月產能衝刺5萬片到Intel矽光子技術突破,從日月光VIPack平台革命到工研院3D IC戰略布局,全球半導體巨擘都在重新校準技術路線圖。這場變革的核心命題是:當傳統的「更小更快」達成成本越來越高時,如何透過「更智慧的整合」開闢新的性能邊界?答案正在先進封裝技術中浮現。而封裝技術也一躍成為主角,甚至將改變半導體市場的格局。

AI應用複雜化 焦點從算力堆疊轉向智慧整合

半導體產業正在經歷一場根本性的邏輯重構。AI應用的複雜化需求正重新定義什麼叫做「高性能」。傳統的單一晶片極致性能追求,已經讓位給系統協同效率的新標準。

當ChatGPT這類大語言模型的參數量突破兆級規模時,單純依靠CPU或GPU的暴力算力已無法滿足需求。AI推理需要CPU處理邏輯判斷、GPU執行並行運算、HBM記憶體提供高頻寬資料存取,三者必須在微秒級別內精密協調。根據IEEE電子封裝學會的最新研究,現代AI系統中CPU、GPU、記憶體的界線正在快速模糊,異質整合已成為AI硬體突破的唯一路徑。

摩爾定律與AI浪潮在此時交匯並非偶然。台積電2奈米製程的研發成本已超過200億美元,是7奈米時代的4倍以上。每一次製程微縮的邊際效益都在遞減,而AI應用對多晶片協同的需求卻在指數級增長。工研院電光系統研究所副所長駱韋仲指出,這種系統級整合的優勢在於可以透過晶片堆疊實現電晶體數量的倍增,達成更強的功能實現。

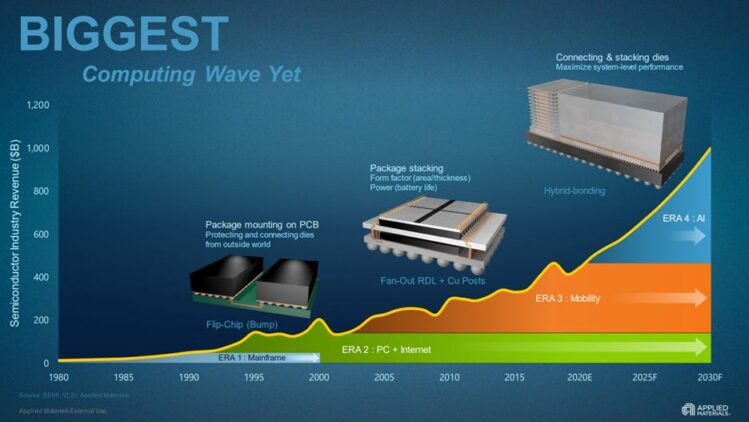

產業競爭邏輯的重構表現在三個層面。技術競爭從「誰能做最小的晶片」轉向「誰能設計最聰明的系統」。成本競爭從「單位性能成本」轉向「系統整體效能成本」。時間競爭從「製程開發週期」轉向「系統整合週期」。當台積電CoWoS產能擴張只需6個月,但3奈米製程良率提升需要18個月時,產業發現了新的競爭武器。先進封裝技術不再是製程微縮的配角,而是與製程並駕齊驅的主角技術。

封裝技術打破晶片邊界 系統級整合開創後摩爾時代新路徑

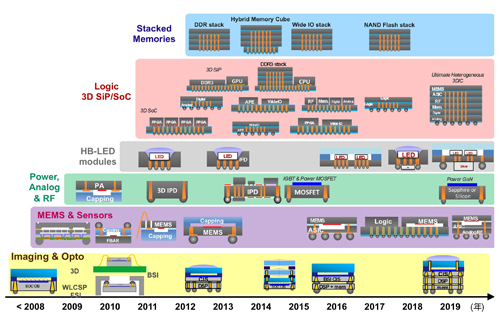

當製程微縮遭遇物理極限,先進封裝技術正在重新定義什麼是性能提升。這不只是技術路徑的調整,而是思維邏輯的根本轉變:從突破單一晶片的邊界,轉向突破整個系統的邊界。

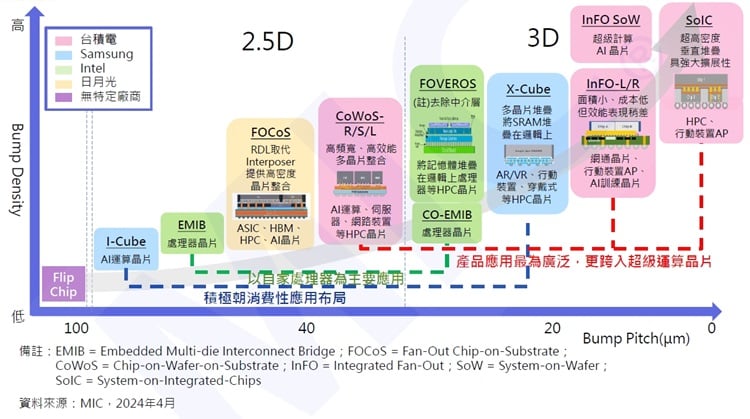

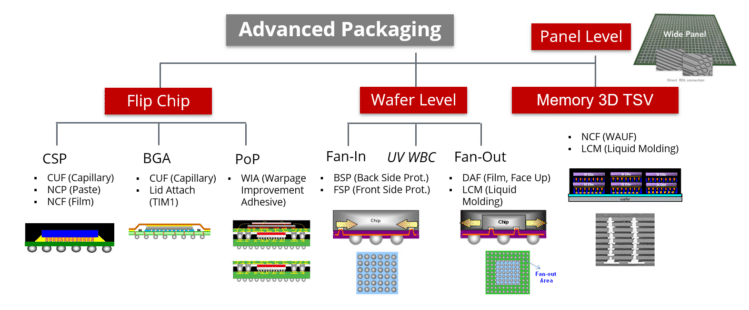

台積電的CoWoS技術體現了這種系統思維的核心。月產能從2023年底的1.8萬片暴增至2024年底的3.6萬片,2025年將衝刺5萬片。透過CoWos封裝,讓多個不同製程節點的晶片能夠「像一顆晶片一樣工作」。輝達H100 GPU整合了800億個電晶體的邏輯晶片與128GB的HBM記憶體,透過CoWoS的矽中介層技術,實現了3.2TB/s的記憶體頻寬,相當於傳統DDR5記憶體的40倍。

日月光的VIPack平台則從另一個角度詮釋系統整合的價值。透過FOCoS、FOCoS-Bridge等六大核心技術,VIPack能夠處理從100×100毫米到更大尺寸的AI晶片模組。日月光半導體銷售與行銷資深副總張尹指出,從5倍矽晶圓尺寸到預計的10倍尺寸需求,考驗的不只是封裝技術,更是系統級的良率控制能力。當面板利用率從傳統300毫米晶圓的57%提升到600毫米大面板的87%時,成本效益的提升將是革命性的。

Intel的EMIB技術展現了差異化競爭的另一種可能。與台積電的矽中介層路徑不同,EMIB採用嵌入式橋接架構,晶圓利用率超過90%,遠高於傳統矽中介層技術的60%。Intel Foundry封裝與測試業務集團副總裁Mark Gardner強調,EMIB的優勢不只在成本,更在於能與矽光子技術深度整合,為光電融合封裝架構奠定基礎。

這些技術突破背後的共同邏輯是:從二維性能極限轉向三維系統可能。這種垂直整合架構不只提升了處理效率,更重要的是大幅降低了功耗。當傳統二維晶片設計逼近物理極限時,三維系統整合為性能提升開闢了全新的空間維度。

設計工具智慧化升級 AI助半導體開發突破瓶頸

當先進封裝技術重新定義硬體架構時,設計工具的革命性升級正在為這場變革提供關鍵支撐。AI技術不只改變了半導體應用,更重要的是開始反哺半導體設計本身,形成「AI設計AI晶片」的正向循環。

設計複雜度的爆炸式增長推動了工具革命的必然性。相較傳統設計,3D IC技術的設計複雜度比傳統晶片提升了至少10倍。每個元件都是獨立製程的產物,還要加上不同材質的中介層,設計路徑的複雜度呈幾何級數增長。更關鍵的是,多物理域問題在3D堆疊環境下變得極其複雜,熱管理和機械應力從次要考量躍升為設計成敗的關鍵因素。

AI技術的引入正在根本性地改變設計方法論。新思科技的Synopsys.ai成為業界首款AI驅動的完整EDA設計套件,能夠自動處理複雜的語法生成,將原本需要資深工程師數週完成的工作壓縮到數小時。西門子推出的AI平台就像懂EDA語法的ChatGPT,在Assembly Verification階段能自動產生驗證語法,大幅降低了人為錯誤的機率。Cadence在異質整合3D-IC技術領域的創新,更是將AI和機器學習技術深度整合到設計流程中。

從人工經驗主導轉向數據智慧主導的方法論革命正在發生。MediaTek與台大電機系合作開發的AI驅動晶片設計演算法,代表了這種轉變的前沿。傳統的設計依賴工程師的經驗和直覺,新的AI驅動設計則能夠在數十萬種可能的設計方案中快速找到最優解。這不只是效率的提升,更是設計品質的質變。

設計工具的智慧化升級具有三重戰略意義。第一是讓複雜的先進封裝設計變得可行且可規模化,原本只有頂尖團隊能夠駕馭的3D IC設計,現在中等水準的工程師也能勝任。第二是大幅縮短了從設計到驗證的週期,在AI晶片競爭白熱化的當下,時間就是最大的競爭優勢。第三是為未來更複雜的系統整合設計奠定了工具基礎,當矽光子、量子晶片等新技術成熟時,AI驅動的EDA工具將是技術落地的關鍵支撐。

光電融合重塑競爭格局 推動台灣從代工轉型系統創新

當電子訊號傳輸逼近物理極限時,光子傳輸正在開啟全新的性能邊界。矽光子技術與先進封裝的融合,不只是技術突破,更是全球半導體競爭格局重塑的歷史機遇。台灣正站在從「代工基地」躍升為「系統創新中心」的關鍵節點。

矽光子技術的戰略意義遠超技術本身。光的速度是電子的300倍,當AI資料中心的運算規模持續擴大時,這個物理優勢變得格外珍貴。台積電在矽光子領域的布局體現了前瞻性的戰略思維,預計2025年完成COUPE(緊湊型通用光子引擎)驗證,2026年整合CoWoS封裝成為CPO(共封裝光學)技術。Intel的策略定位與眾不同,將CPO視為與EMIB和Foveros技術互補而非競爭的技術,形成光電融合的系統解決方案。

台灣在這波技術變革中的優勢正在從製程微縮時代的「代工優勢」轉化為封裝時代的「系統整合優勢」。SEMI矽光子產業聯盟匯聚了超過30家台灣廠商,從台積電、日月光的龍頭企業到聯亞、華星光的專業廠商,形成了完整的產業生態。根據SEMI數據,2025-2030年間全球矽光子半導體市場將以年複合增長率25.7%的速度成長至786億美元,台灣廠商在InP磷化銦雷射磊晶片代工領域的市佔率高達八成。

全球競爭格局的重塑正在加速進行。NVIDIA計劃2026年推出Spectrum-X矽光子交換器,Broadcom、Marvell等國際巨擘都在大舉投入CPO技術研發。更值得關注的是,挪威主權基金在2025年大幅增持台灣矽光子概念股,光聖持股占比從1.17%增加至3.27%,增長將近200%。國際資本的布局反映了對台灣技術路線的深度認同。

台灣面臨的戰略機遇是歷史性的。在製程微縮時代,台灣是技術的執行者;在系統整合時代,台灣有機會成為技術標準的制定者。工研院推動的research foundry概念,提供先進封裝的研究平台,讓全球研發單位可以在台灣進行前瞻技術驗證。這種模式如果成功,將讓台灣從「代工服務提供者」升級為「技術創新引領者」。

矽光子技術的產業化進程正在加速。台積電已完成1.6T光引擎並展開3.2T測試,智邦等網通設備廠商已在2020年開始投入CPO技術研發。隨著800G/1.6T光收發模組在2025-2026年間實現顯著成長,CPO技術預計在2026年後逐步發揮影響力。當高階AI應用領域開始採用CPO取代傳統高速光收發模組時,掌握關鍵技術的台灣廠商將在全球競爭中占據最有利的戰略位置。

這場技術典範轉移的最大啟示是:當傳統競爭優勢遭遇天花板時,產業創新往往來自跨領域的整合突破。半導體產業以系統整合創新回應製程極限挑戰,台灣站在這個歷史轉折點上,擁有從「製造強國」升級為「整合強國」的戰略機遇。

面對2026年CPO技術商業化的關鍵節點,台灣必須完成三大戰略布局:技術層面,加速矽光子產業鏈本土化,確保在光電融合時代的技術自主權;人才層面,培育跨電子、光學、封裝的系統整合人才,建立新時代的競爭優勢;生態層面,強化與美歐日的技術聯盟,在全球標準制定中爭取更大話語權。

歷史將會記住2025年:這是半導體產業競爭邏輯發生根本轉變的一年,也是台灣半導體產業從「代工時代」邁向「整合時代」的起點。在這個新時代,勝負不再取決於誰能做出最小的晶片,而是誰能設計出最聰明的系統。當摩爾定律的傳統路徑成本越來越高,讓業界越來越難以負擔,基於先進封裝的異質運算系統整合也一躍成為持續推動半導體產業進化的重要關鍵,讓晶片設計走向另一個全新的疆界。